芯盟科技发布基于HITOC™ 技术的3D 4F² DRAM架构

2022年6月14日,在中国国际半导体技术大会(CSTIC) 2022上,芯盟科技CEO洪沨博士在主题演讲中,发布了基于HITOC™技术的3D 4F² DRAM架构。这是芯盟科技继2020年发布的存算一体AI芯片“SUNRISE”之后,在单芯片异构集成技术领域的又一次重大创新突破。

当前DRAM技术的挑战

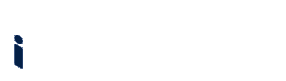

为了追求极致的芯片面积利用率,各大DRAM厂商利用先进半导体工艺尽可能地缩小单个Array晶体管面积,当前主流DRAM产品技术节点为1z,随着晶体管尺寸的持续微缩,对芯片的工艺及设计带来了以下一系列新的挑战:

① 更高的设计要求,尺寸微缩使得位线电容增加的同时SN电容降低,这样感应冗余度(Sensing Margin)随之减小;

② 更低的功耗,当今社会便携设备的应用无处不在,对降低功耗的需求将一直存在;

③ 更低的漏电流,尺寸微缩带来的短沟道效应以及更薄的高K介质材料必然会引发更高的漏电流,如何降低漏电流是DRAM工艺和设计的关键挑战;

④ 更低的工艺成本,尺寸微缩意味着需要使用大量先进的半导体制程,如SADP、SAQP、EUV、高深宽比刻蚀等等,如何尽量减少这些工艺的使用次数是DRAM工艺制程的关键挑战。

芯盟科技基于HITOC™ 技术的3D 4F2 DRAM架构

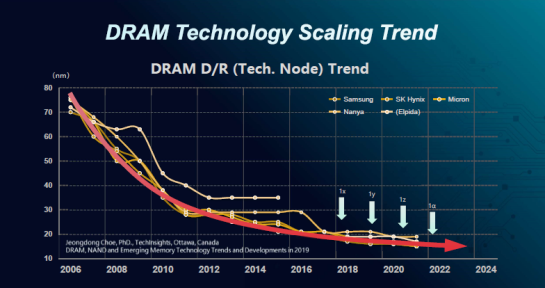

什么是HITOC™技术?

芯盟科技的HITOC™(Heterogeneous Integration Technology On Chip)技术,运用先进的晶圆对晶圆(Wafer-on-wafer)和晶粒对晶圆(Die-on-Wafer)混合键合(Hybrid Bonding)制造工艺,将不同类型的wafer或die上下对准贴合,以实现真正的三维异构单芯片集成。

芯盟科技当前基于Wafer-on-wafer的HITOC技术产品,已经广泛应用于多个市场领域。基于Die-on-Wafer以及Multi-Wafer-on-Wafer的三维堆叠产品也正在研发之中。

基于HITOC™ 技术的3D 4F² DRAM

芯盟科技将HITOC™技术创新性地应用到了先进DRAM开发中,创造了一种全新的3D 4F² DRAM架构。

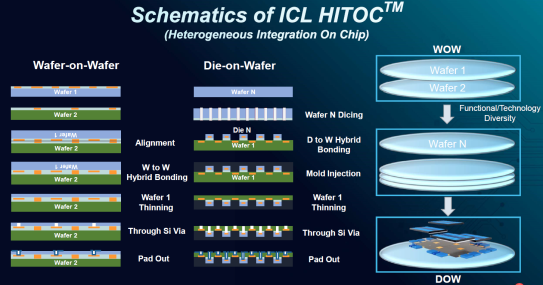

首先,芯盟科技创新性地设计并实现了垂直沟道阵列晶体管(VCAT)。如下图所示:

此VCAT架构中晶体管采用了镜像设计,相邻两个晶体管中心对称,其中单晶硅体之间通过绝缘材料结合气隙隔绝的方法分隔开来,同时通过高精度光刻及刻蚀工艺严格控制单晶硅沟道的厚度,保证其厚度小于一定数值以使此晶体管在开启时沟道为全耗尽型,大大降低了DRAM固有缺陷“Row Hammer”效应的影响。

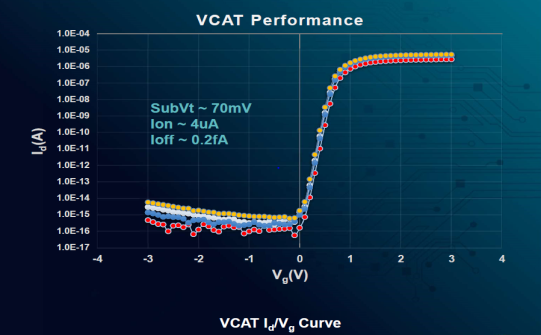

通过测试可以看出,HITOC™ DRAM架构下的晶体管的开启电流达到了DRAM SN充电的要求(4μA),而漏电流(0.2fA)也可满足晶体管在关态时的要求,同时70mV/DEC的亚阈值摆幅也体现了晶体管良好的开关特性,测试结果如下图所示:

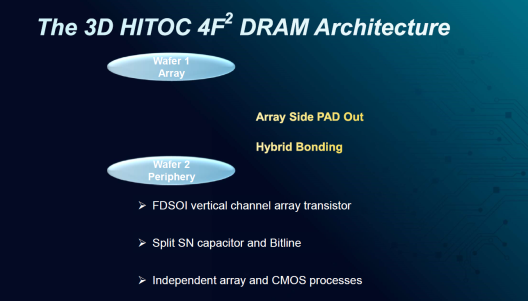

然后,我们利用三维HITOC™技术的特点,将存储单元在Array Wafer中垂直竖起并把存储单元电容和位线置于Array Wafer 的上下两边,这是4F² 能够真正实现的关键因素。

再者,我们将传统DRAM架构中的存储阵列Array和主要的CMOS 逻辑电路分开设计,分别制造在两片独立晶圆上,最终用HITOC™技术集成为3D 4F² DRAM单芯片。

芯盟的3D HITOC™ 4F² DRAM架构具有以下重要优势:

① 更低的位线电容,提升了感应冗余度,降低了CMOS设计的难度;

② 更低的字线延迟,使得高频率DRAM设计更加简单;

③ 更好的CMOS性能,由于CMOS独立在一片晶圆上设计,不受Array工艺制程的限制,具有更充分的发挥空间;

④ 更低的成本,该架构的单个Array晶体管面积与传统DRAM相比减少了33%,且制程与当前半导体工艺完美兼容,所需的SADP工艺次数较传统工艺大大减少,无需昂贵的SAQP及EUV工艺;

⑤ 更好的技术延展性,传统DRAM的发展受限于在尺寸微缩的同时SN(Storage Node)电容值下降过快,导致设计难度增大,HITOC™ DRAM架构设计对SN电容值的敏感程度更低,SN的制程复杂程度及高K介质的K值要求均低于传统DRAM架构,所以未来HITOC™ DRAM的微缩空间更大。

芯盟的3D HITOC™ 4F² DRAM架构为先进DRAM技术和产品的持续优化发展提供了一条更加宽阔的赛道。

关于芯盟科技

芯盟科技成立于2018年,总部位于浙江海宁,在上海张江设有研发中心。公司致力于成为客户信赖的异构集成芯片产业引领者,专注于三维异构集成芯片架构设计及系统整合,提供基于三维异构集成架构的芯片系统技术服务和硬件实施。