突破| 绕过EUV光刻机来实现DRAM芯片自主开发,这家存算一体芯片公司成功实现

-- 转载来源:微信公众号“问芯Voice”--

DRAM 技术一直发展到 10nm 制程以下,导入 ASML 独门秘技极紫外线 EUV 光刻机已是业界共识。现今韩系存储大厂三星、SK 海力士,以及美系存储大厂美光都朝此方向前进; 三星的 14nm DRAM 开始导入 EUV 技术进入量产、SK 海力士使用 EUV 生产 1a 制程的 DRAM、美光也将在 10nm 的 1γ 节点中导入 EUV 光刻技术。

谈到一台一亿欧元天价的 EUV 机台,绝对会触碰到国内半导体产业心中的“共同遗憾”。

若说半导体产业有哪些卡脖子的技术,EUV 光刻机无法进口到国内,足以让国内先进制程芯片的制造“致命”。在逻辑制程(晶圆代工)方面,已经让中芯国际退居到 14nm、28nm 制程,暂时把 7nm 制程以下的先进制程制造放一边。

在存储技术方面,国内的 NAND Flash 技术可以尽情冲刺追赶国际大厂的水平,是因为 3D NAND 堆叠技术的特性不需要用到 EUV 机台。反之,当 NAND Flash 晶体管从 2D 变成 3D 架构,对于半导体设备的最大转变,是需要用到大量的薄膜机台和等离子刻蚀机台,EUV 光刻机反而不是主角。这一点给了中国 NAND Flash 技术的追赶机会。

发展 DRAM 技术,有没有可能做到完全不需要用到 EUV 光刻机,就可以做出比肩三星、SK 海力士、美光等国际大厂的技术水平? 这个技术方向在过去,答案或许是否定的。不过,日前一家新型存算一体芯片技术公司的技术突破,或许会让所有的不可能,转换为无限可能。

在刚刚举行的中国国际半导体技术大会 CSTIC 2022 中,芯盟科技 CEO 洪沨在会议中宣布了基于 HITOC 技术的 3D 4F² DRAM 架构的问世。

“基于 HITOC 技术的 3D 4F² DRAM 架构”,对外界而言是非常陌生的技术。在解释何为 HITOC 技术?以及何为 3D 4F² DRAM 架构之前,先来提出一个非常关键点:基于 HITOC 技术所开发的全新架构的 3D 4F² DRAM 芯片,最大特点是不需要用到 EUV 光刻机,也不需要多重图形曝光 SAQP(Self-Aligned Quadruple Patterning)的步骤,这可以大幅减少成本,更重要的是,避免技术往前突破的同时,设备被国外制造商卡脖子。

这是芯盟继 2020 年发布存算一体 AI 芯片 SUNRISE 后,在单芯片异构集成技术领域,又一次的重大创新突破。

芯盟在 2020 年 9 月首次发布全球第一款基于 HITOC 架构的高性能存算一体 AI 芯片 SUNRISE,此芯片目前已成功应用于晶圆厂生产线智能缺陷分类系统领域。 再者,高性能计 HPC 公司豪微科技在最新流片成功的布谷鸟 2(cuckoo 2)芯片上,采用的芯盟的HITOC技术,实现了大容量存算一体 3D 架构。

芯盟这次把 HITOC 技术架构,使用在 DRAM 设计上。

什么是 HITOC 技术?

芯盟科技表示,HITOC 技术(Heterogeneous Integration Technology on Chip)技术是运用先进的晶圆对晶圆(Wafer-on-Wafer)和晶粒对晶圆(Die-on-Wafer)混合键合(Hybrid Bonding)制造工艺,将不同类型的 wafer 或 die 上下对准贴合,以实现真正的三维异构单芯片集成。

芯盟科技当前基于 Wafer-on-Wafer 的 HITOC 技术产品,已经导入市场应用,Die-on-Wafer 和 Multi-Wafer-on-Wafer 的 3D 堆叠产品正在研发中。

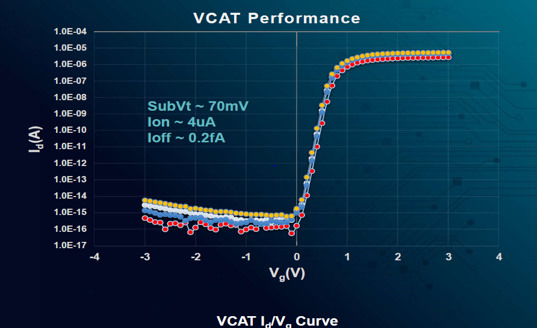

芯盟也将 HITO C技术应用到先进 DRAM 开发中,提出一种全新的 3D 4F² DRAM 架构。首先,芯盟创新性地设计并实现了垂直沟道阵列晶体管(VACT)。

VACT 架构中的晶体管采用了镜像设计,相邻的两个晶体管中心对称。其中单晶硅体之间通过绝缘材料结合气隙隔绝的方法分隔开来,同时通过高精密度光刻和刻蚀工艺,严格控制单晶硅沟道的厚度,保证其厚度小于一定数值以使此晶体管在开启时沟道为全耗尽型,降低了 DRAM 缺陷 “Row Hammer” 效应的影响。

然后,是利用三维 HITOC 技术的特点,将存储单元在 Array Wafer 中垂直竖起,并把存储单元电容和位线置于 Array Wafer 的上下两边,这是 4F² 能够真正实现的关键因素。

再者,将传统 DRAM 架构中的存储阵列 Array 和主要的 CMOS 逻辑电路分开设计,分别制造在两片独立的晶圆上,最终用 HITOC 技术集成为 3D 4F² DRAM 单芯片。

芯盟也简述了 3D HITOC 4F² DRAM 架构的几项重要优势:

第一,更低的位线电容,提升了感应冗余度,降低了 CMOS 设计的难度;

第二,更低的字线延迟,使得高频率 DRAM 设计更加简单;

第三,CMOS 独立在一片晶圆上设计,不受Array工艺制程的限制,具有更为充分的发挥空间;

第四,更低的成本,该架构的单个 Array 晶体管面积和传统 DRAM 相比减少 33%,且制程和当前半导体制程兼容,所需的双重曝光 SADP 工艺次数较传统工艺大大减少,无须昂贵的多重曝光 SAQP 和 EUV 工艺;

第五,更好的技术延展性,传统 DRAM 的发展受限在大尺寸微缩的同时,SN(Storage Node)电容值下降过快,导致设计难度增大,HITOC DRAM 架构设计对 SN 电容值的敏感度更低,SN 制程复杂度和高K介质的K值要求均低于传统 DRAM 架构,所以未来 HITOC DRAM 的微缩空间更大。

从目前的信息可知,基于创新的 HITOC 技术的 3D 4F² DRAM 架构,从后端封装另辟蹊径,可以走出一条与传统 DRAM 架构不一样的道路。但目前还不知道的另一个关键点是:利用 HITOC 技术 3D 4F²设计生产出来的 DRAM芯片,可以对标到国际大厂多少纳米nm的技术?可以直接进入10nm以下吗?

一来可以避免传统 DRAM 设计和制造上的专利壁垒,二来不需要 EUV 光刻机不但可以大幅节省生产成本,更可以避开国际大厂卡脖子的状况,对于现阶段的芯片技术发展,会是一个很重要的突破信号点。