三维异构系统集成 — 技术创新引领芯片性能时代

2022年7月5日,苏州金鸡湖畔,在由《半导体芯科技》杂志社主办的《第十届晶芯研讨会---拓展摩尔定律:先进半导体制造与封装技术协同发展大会》上,芯盟科技资深副总裁洪齐元先生做了名为《三维异构系统集成 — 技术创新引领芯片性能时代》的演讲。在演讲中,洪先生向与会嘉宾介绍了芯盟科技、HITOC™技术及其芯盟三维异构系统集成业务的最新进展。

芯盟科技独有的HITOC™技术

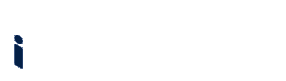

近年来随着集成电路各维度发展的技术和成本限制,沿着摩尔定律前进的道路愈发崎岖,CPU的频率和性能提升幅度变小,DRAM在现有架构下也很难向极致的先进工艺节点步进。内存墙、功耗墙,以及先进工艺制程的限制愈发成为痛点。而芯盟科技独有的HITOC™(Heterogeneous Integration Technology on Chip)技术,使摩尔定律在三维结构上得以延续,从而引领三维芯片这一全新赛道。

芯盟科技的HITOC™技术区别于传统的先进封装,其运用先进的混合键合(Hybrid bonding)集成电路制造工艺技术,将不同类型、不同结构甚至不同工艺节点的芯片集成为一体。最典型的应用场景就是将多功能SOC芯片与分布式DRAM芯片上下集成为一块超高性能单芯片,相比传统SOC外接 DDR以及使用基于HBM的2.5D先进封装方式,HITOC™技术极大的增加了连线密度和数量,省去了PHY接口并大大缩短了连线长度,从而可以显著地减少系统功耗和面积,大大提高存储带宽,进而打通内存瓶颈,使芯片系统整体运算性能大大增强。

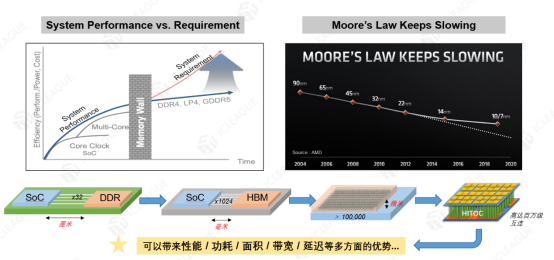

HITOC™技术主要有Wafer-on-Wafer(晶圆对晶圆)、和Die-on-Wafer(芯片对晶圆)两种技术路线。

以逻辑晶圆对DRAM晶圆为例,经过芯片设计和工艺的集成整合,通过Hybrid Bonding(混合键合)将逻辑晶圆和DRAM晶圆连在一起之后,经减薄,做硅通孔金属引出,再进行切割封装之后,与单芯片没有不同。 芯片对晶圆技术则是通过将切割筛选出的不同芯片 键合堆叠在另一晶圆上,然后通过注塑、减薄、硅穿孔、金属线引出等工艺来实现高性能复杂芯片系统。晶圆对晶圆技术的芯片产品已经非常成熟并已在大规模量产中。多片晶圆对晶圆和 芯片对晶圆堆叠技术研发也将在今年年底基本完成。

早在2020年9月,芯盟科技就发布了全球第一款基于HITOC™架构的高性能存算一体AI芯片- SUNRISE,此芯片目前已成功应用于晶圆厂生产线智能缺陷分类系统领域。 在今年6月的中国国际半导体技术大会(CSTIC) 2022上,芯盟科技CEO洪沨博士发布了基于HITOC™技术的全球首款VCAT 3D 4F² DRAM架构。由此可见,芯盟科技已经在多个应用维度上,创新性的运用HITOC™技术,引领芯片产品向真正的三维架构变革。

芯盟科技的三维异构系统集成业务

三维异构系统集成是芯盟科技的一大核心业务,旨在为客户在大算力、高带宽、低功耗等产品领域提供一整套三维异构系统集成服务,以提升产品价值。

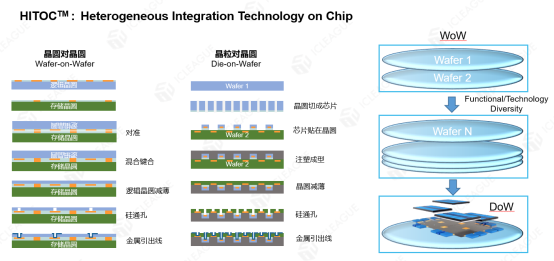

芯盟的SOH™(System On HITOC™)系统集成解决方案,可以覆盖芯片从设计到量产所需的全流程,以帮助客户完成三维异构集成芯片设计及系统整合,包括异构集成技术的设计咨询服务、基于异构集成技术的芯片架构/DFT/中后段解决方案、晶圆/芯片级混合键合的设计和制造解决方案,以及相关IP的开发和授权业务。

参照上图以Logic + DRAM的三维集成为例:

从芯片设计架构,依次到RTL、Netlist以及后端设计启动,便分别开始Logic、DRAM、混合键合三部分的设计和 GDS的产生,再到Logic和DRAM Fab流片,到Hybrid Bonding Fab键合生产,最终封装测试后交付给客户验收。在整个流程当中,芯盟科技可以为客户提供基于HITOC™技术的整套集成设计服务,包含芯片架构、设计、可测性、后端服务以及热仿模型解决方案;同时也可以提供两片到多片晶圆间的混合键合设计和制造解决方案、HITOC™系统封装测试、先进制造及设计咨询和培训等细分服务。当然,芯盟科技也可以提供Logic + DRAM、Logic + Logic以及Logic + SRAM等不同堆叠形式产品的设计服务和产能预定和相关流片服务。

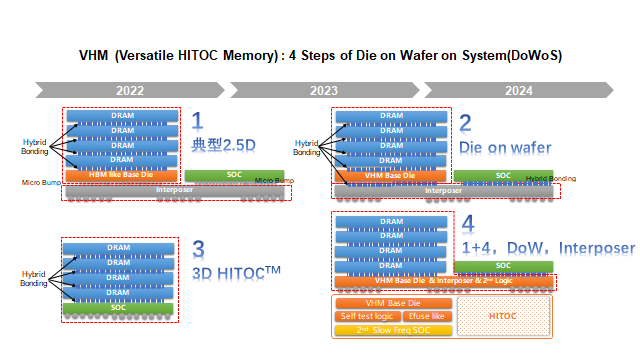

作为三维芯片的重要组成部分,芯盟科技同时可以提供相关的IP开发和授权服务,例如,VHM(Versatile HITOC™ Memory)、HDC(HITOC™ DRAM Controller)以及Backside TSV、TSV、SRAM等IP,其他更多重量级IP的三维化同时正在进行中,后续也将陆续提供给客户。

芯盟科技的三维异构系统集成产业生态已经非常成熟,可以为客户提供成熟的HITOC™ 3D Design Kit 、Work Flow、方法学及参考设计文档。芯盟科技有成熟稳定的混合键合 Fab资源,以及逻辑晶圆和特别可定制化的DRAM 晶圆资源,以满足客户从工程验证3D芯片架构到大规模量产的各种需求。

除了3D解决方案,芯盟科技还可以为客户提供基于VHM(Versatile HITOC™ Memory)技术的2.5D解决方案。参照上图,其可合作的产品形式非常灵活,包括:

1.HBM Like 高带宽DRAM解决方案(可替代HBM 且更有带宽和成本优势);

2.Process in Memory解决方案(提供标准Memory接口,客户可定制加速逻辑在Memory中);

3.Custom SOC解决方案(作为协处理器和SOC合封在一起,提供额外的高算力特性);

4.eDRAM 解决方案(提供介于Last Level Cache和Main Memory之间的一个高密度高速存储)。

--原创声明:本文为芯盟原创作品,未经授权,严禁转载!--